# Single Spin Wireless Architecture of nm Priority Resolver

Dr. J. Gope (MIEEE, CE), S. Chowdhury (Kolay), S. Samajpati, B. Kar ECE Dept., Camellia School of Engineering & Technology, MAKAUT, India

**ABSTRACT:** Priority resolver is ubiquitous in digital logic circuits as it is frequently used to optimize large number of inputs into a minimum number of outputs. This particular circuit exclusively demonstrate manifestation of outputs, controlled by the priority of logic interventions of the inputs. CMOS Logic made circuits with higher number of inputs experiences an excessive power dissipation. On the other hand, Single Spin Logic (SSL) offers low power dissipation, high speed, high packing density in circuit design. It is a novel approach in device vicinity that involves the spin polarity of electron rather only the charge. Thus the authors motivated themselves to design SSL based priority resolver. This technical note presents a pragmatic view of priority resolver design using SSL.

Keywords: Not wired, power dissipation, priority resolver, resolver, Single Spin Logic (SSL).

## I. INTRODUCTION

In modern technology, cramping of circuits has become a greatest challenge to the researchers. To achieve such requirement some technological shift has been incorporated. Few design techniques are already in use such as Carbon Nano Tubes (CNT), Rapid Single Flux Quantum (RSFQ), Resonant Tunneling Devices (RTD), Quantum Dots (QD), CMOS [1] and so on.

But these all are based on electron charges or conveniently these are simple charge coupled devices which suffers from leakage power. To prevail over such difficulty Prof. Supriyo Bandopadhyay of Virginia Commonwealth University conceptualized a new idea known as spintronics [2]. In spintronics, The information is carried out by using electron spin rather than electron charge. This ensures Spin degree of freedom in electronic circuits. Eventually, Sarkar et.al.[3], has applied the spin property in logic designing and a new term evolved known as 'Single Spin Logic'.

SSL has already being used in different logical circuits, such as NAND gates (H. Agarwal et.al.) [4], Full Adder (Soumitra Shukla et.al.) [5], Divider (Bahniman Ghosh et.al.) [6] and so on.

In the midst of different combinational circuits resolver is brilliant topography combining various aspects of fetching the outputs such as navigation, interrupt request control and so on. Thus a bucket full of research relevance on priority resolver is omnipresent [7]. Authors here have motivated themselves to realize a priority resolver circuit by using SSL, where the output depends upon the highest prioritized input.

### II. SSL BASED LOGIC REALIZATION

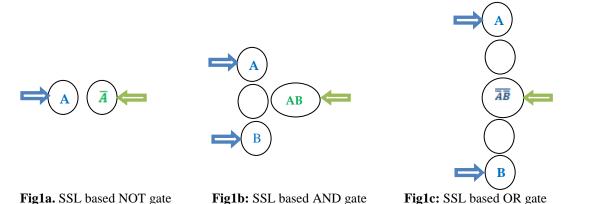

Digital logic family has grown up depending upon three basic gates such as NOT, AND and OR gates. The SSL based designing of the above mentioned gates are described in Fig 1a to Fig 1c.

In the above mentioned figures A and B are two inputs which are represented by blue arrows and corresponding outputs are represented by green arrows.

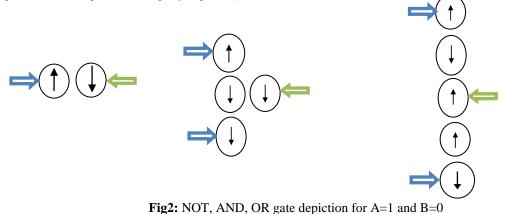

Fig 2 represent the NOT, AND and OR gates using input A as up spin (which signify logic '1') and input B as down spin(which signify logic '0')

### **III. PRIORITY RESOLVER**

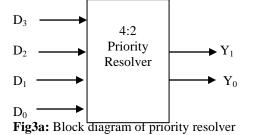

In digital electronics resolver plays a great role. Resolver selects any one inputs from it's 2n inputs and flaunt it by using its n outputs lines. In this encode users suffer from some typical problems when more than one inputs are activated. To triumph over such problems priority resolver evolves. In priority resolver the output not only depends upon the inputs but also maintain the priority (highest priority to the MSB) of the inputs. The block diagram and truth table of a 4:2 priority resolver is given in the Fig3a and Fig3b respectively.

| Inputs         |                |                |                | Outputs |       |

|----------------|----------------|----------------|----------------|---------|-------|

| D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | $Y_1$   | $Y_0$ |

| 0              | 0              | 0              | 0              | Х       | Х     |

| 0              | 0              | 0              | 1              | 0       | 0     |

| 0              | 0              | 1              | Х              | 0       | 1     |

| 0              | 1              | Х              | Х              | 1       | 0     |

| 1              | Х              | Х              | Х              | 1       | 1     |

Fig3b: Truth table of priority resolver

#### IV. SSL BASED PRIORITY RESOLVER

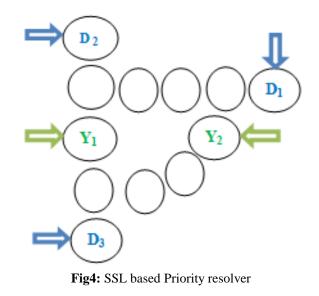

The logical illustration of priority resolver is given in Fig4 where blue lines depict the inputs and green lines depict the output. In 4:2 priority resolver  $D_3$ ,  $D_2$ ,  $D_1$  and  $D_0$  are the inputs and  $Y_1$  and  $Y_0$  are the two inputs where  $Y_1 = D_3 + D_2$  and  $Y_0 = D_3 + \overline{D}_2 D_1$

Fig5 represents the pictorial view of a priority resolver by taking some specified inputs such as  $D_3 = 0$ ,  $D_2 = 1$ ,  $D_1 = 0$  and  $D_0 = 1$ .

Fig5: Priority resolver using up spin and down spin representation.

#### V. CONCLUSION

From the above discussion we can conclude SSL based design provides fastest speed, low cost, light weight nm range ICs which can be integrated in future digital logic designing. The next generation SSL priority resolver is sure to driven out the complexities of CMOS made priority resolver.

#### **ACKNOWLEDGEMENTS**

The authors wish to thankfully acknowledge the financial contribution made by CSET, Barasat in continuing this research.

#### REFERENCES

- [1] Dr. Jayanta Gope et.al.,"Hybrid CMOS-SET Decision Making Nano IC: A Case Study", International Journal of Science, Engineering and Technology Research (IJSETR), Volume 4, Issue 6, June 2015.

- [2]

- Marc Cahay, Supriyo Bandyopadhyay, "An electron's spin---Part I', Potentials, IEEE, 2009. Subir Kumar Sarkar et.al., "SPINTRONICS DEVICE BASED POWER EFFICIENT VLSI CHIP DESIGN FOR [3] UNIVERSAL CODE CONVERTER", Canadian Journal of pure & applied science, SENRA Academic Publishers, Burnaby, British Columbia, Vol.2, No.3, pp 595-600, 2008, IISN: 1715-9997.

- H. Agarwal et.al.,"Single spin universal Boolean logic gates", IOP Publishing and Deutsche Physikalische [4] Gesellschaft, New Journal of Physics, volume 10, January 2008.

- Soumitra Shukla et.al, "1-BIT FULL ADDER IMPLEMENTATION USING SINGLE SPINLOGIC PARADIGM", [5] World Scientific Journal, Spin, Volume 2, Issue 2, 10.1142/S2010324712500129.

- Bahniman Ghosh et.al., "2-Bit Divider Circuit Implementation Using Single Spin Logic Paradigm " Article in [6] Journal of Computational and Theoretical Nanoscience11(11) November 2014.

- Preeti Panchal et.al., "Design of 8-bit Dynamic CMOS Priority Resolvers based on Active-Low Logic", Proceedings [7] paper, International Conference on Electronics and Communication Systems, 2013.